In this guide series, we shall take a look at the cache in ARM Cortex M7 MCU and how to handle them properly later.

In this part of the guide series, we shall cover the following:

- Introduction to the cache.

- Cache architecture.

1. Introduction to the Cache:

In modern embedded systems, performance and efficiency are critical factors that determine the success of applications ranging from consumer electronics to industrial automation. One key component that significantly enhances the performance of these systems is the cache. Caching is a technique used to reduce the time the CPU spends accessing data from the main memory, thereby speeding up execution and improving overall system efficiency.

Purpose of Caching

The primary purpose of caching is to store frequently accessed data and instructions closer to the CPU, allowing for faster retrieval. This is particularly important in real-time and embedded systems where latency and speed are crucial. By reducing the time needed to fetch data from the slower main memory, caches can dramatically enhance the performance of the system.

Importance in Embedded Systems

In embedded systems, the need for low-latency data access is paramount. Applications such as motor control, digital signal processing, and complex sensor interfacing require quick and predictable access to data and instructions. Efficient use of cache can also contribute to lower power consumption, which is a critical consideration in battery-powered and energy-sensitive applications. By minimizing the number of accesses to the main memory, which consumes more power than the cache, overall energy efficiency can be improved.

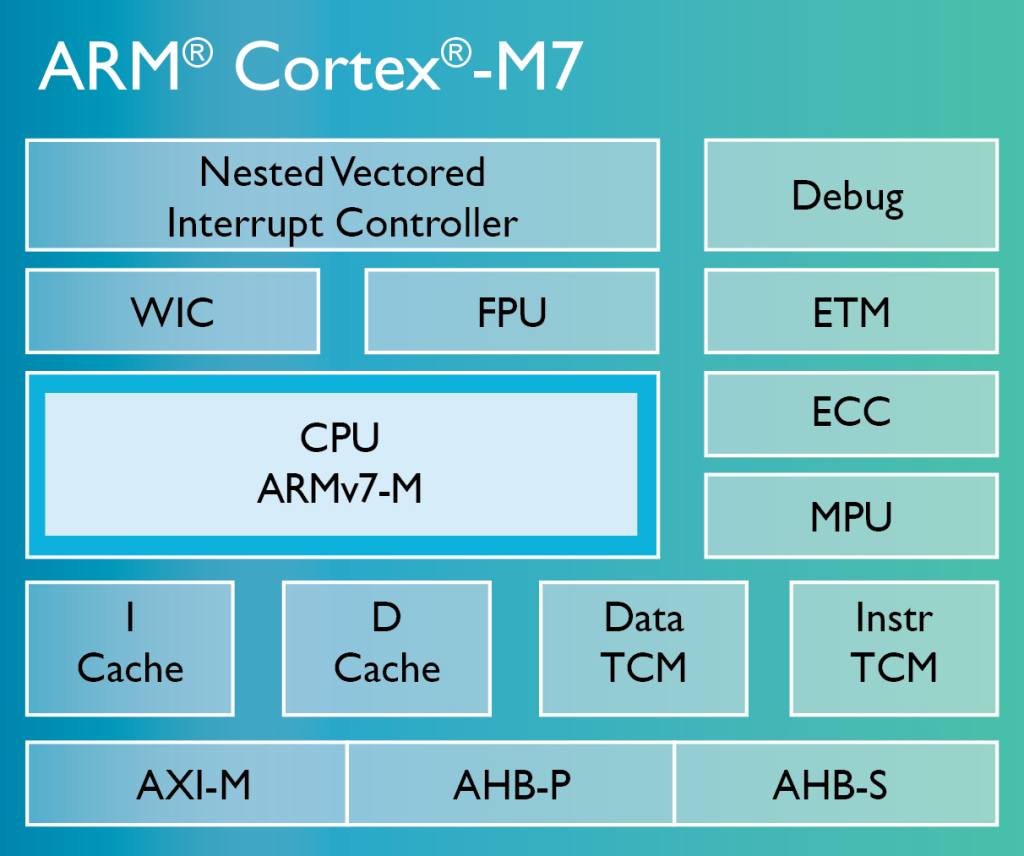

ARM Cortex-M7 Overview

The ARM Cortex-M7 is a high-performance microcontroller designed to meet the demands of computationally intensive applications. Featuring a dual-issue pipeline, advanced branch prediction, and high clock speeds, the Cortex-M7 is equipped to handle complex tasks with ease. One of the standout features of the Cortex-M7 is its Harvard architecture, which uses separate instruction and data buses. This architecture is complemented by the inclusion of separate instruction and data caches, which play a pivotal role in its performance capabilities.

Role of Cache in Cortex-M7

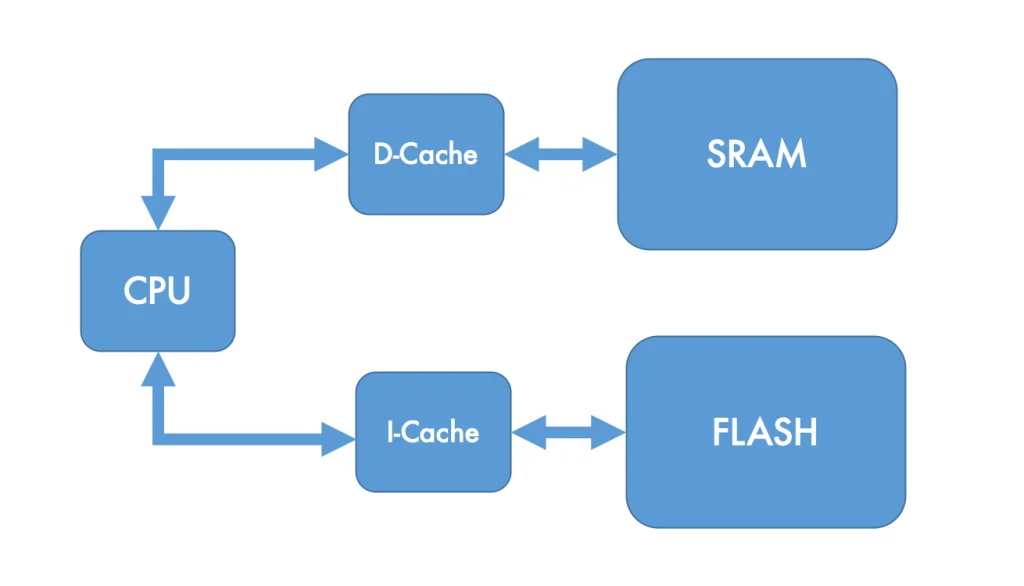

In the ARM Cortex-M7, the cache system is crucial for maximizing performance. The instruction cache (I-Cache) and data cache (D-Cache) work independently to store instructions and data, respectively. This separation allows for simultaneous access, reducing bottlenecks and ensuring that the CPU has quick access to the necessary information. By leveraging these caches, the Cortex-M7 can execute instructions and process data more efficiently, making it ideal for high-speed, real-time applications.

In this article, we will explore the cache architecture of the ARM Cortex-M7 in detail, covering its structure, operation, and the various policies that govern its behavior. Understanding these aspects is essential for optimizing performance and achieving the best results in embedded system applications.

2. Cache Architecture in ARM Cortex-M7:

Harvard Architecture

The ARM Cortex-M7 employs a Harvard architecture, which means it has separate buses for instructions and data. This separation allows the CPU to access instructions and data simultaneously, enhancing overall performance and efficiency.

Instruction Cache (I-Cache)

- Size and Associativity: The I-Cache typically ranges in size from 16 KB to 64 KB and is 4-way set-associative.

- Function: The I-Cache stores instructions fetched from the main memory, allowing the CPU to execute instructions more quickly. By keeping frequently used instructions in the cache, the system reduces the need for repeated memory accesses.

- Line Size: Each line in the I-Cache is typically 32 bytes.

Data Cache (D-Cache)

- Size and Associativity: Similar to the I-Cache, the D-Cache also ranges from 16 KB to 64 KB and is 4-way set-associative.

- Function: The D-Cache stores data read from or written to the main memory, decreasing data access latency. This is crucial for operations that require frequent data reads and writes.

- Line Size: The line size is also typically 32 bytes.

- Write Policy: The D-Cache commonly uses a write-back policy, meaning data is first written to the cache and later written back to the main memory, improving write efficiency.

Cache Controller

- Control Registers: The cache controller manages both the I-Cache and D-Cache through a set of control and status registers. These registers can enable or disable the caches, configure cache operations, and provide status information.

- Maintenance Operations: The cache controller supports various maintenance operations, including:

- Invalidate: Removing entries from the cache.

- Clean: Writing back dirty cache lines to the main memory.

- Clean and Invalidate: Combining both operations to ensure data consistency.

Memory Protection Unit (MPU) Integration

- MPU Regions: The MPU can define memory regions with specific cache policies, such as cacheable or non-cacheable regions.

Cache Coherence and Consistency

- Coherence: Ensures that data in the cache is consistent with the main memory, particularly important in systems with DMA or peripherals that access memory directly.

Performance Considerations

- Latency Reduction: The primary goal of the caches is to reduce latency for both instruction fetches and data accesses.

- Throughput Improvement: By keeping frequently accessed data and instructions in the cache, the overall system throughput is improved.

- Impact of Cache Misses: A cache miss, when the CPU requests data not present in the cache, results in fetching the data from the main memory, which introduces latency and affects performance.

In part 2, we shall cover the cache policies and how the cache work for reading and writing.

Stay tuned.

Happy coding 😉

Add Comment