In this guide, we shall take a look at the memory types in ARM Cortex M7 and the attribute the of the MPU.

This guide shall cover the following:

- Memory types.

- MPU attributes.

- Important tips.

- MPU configurations.

4. Memory Types:

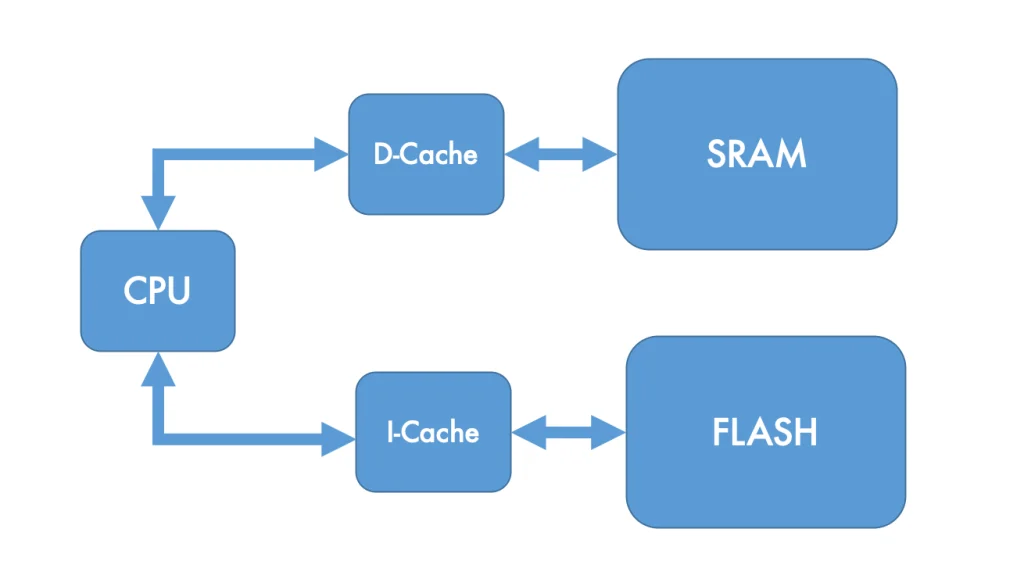

The memory in ARM Cortex M7 is classified as following:

- Normal Memory.

- Device Memory.

- Strongly ordered Memory.

- Normal memory is good for code execution.

- It allows the speculative access.

- No speculative access in strongly ordered and device memories.

- CPU waits for the end of instruction before performing another one.

- Each write needs to be visible for device, eg- external NAND.

- Device memory is used for microcontroller Registers.

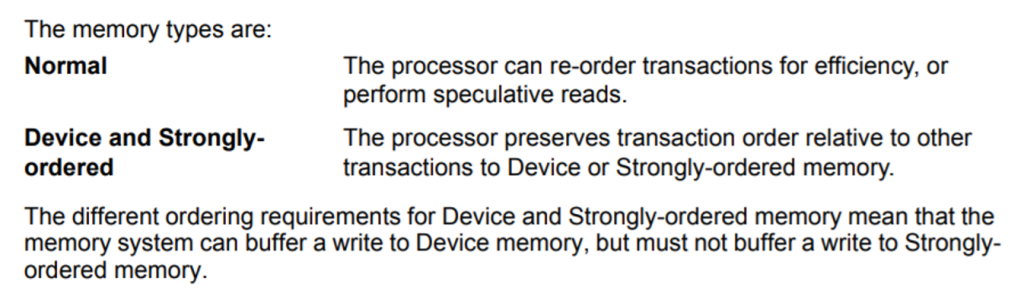

Here is the default memory access behavior for ARM Cortex M7:

5. MPU Attributes:

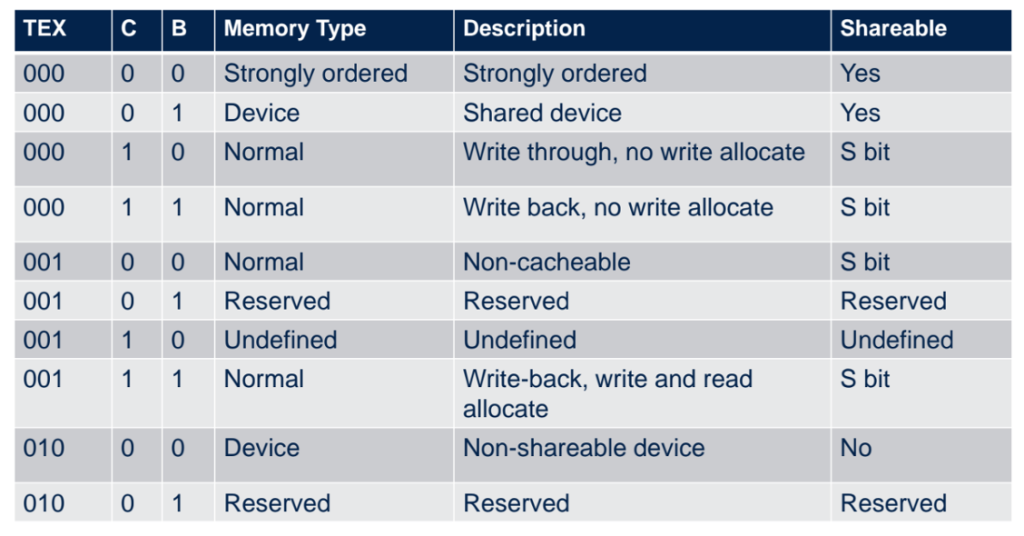

The MPU attributes in ARM Cortex M7 have the following:

- Shareability.

- Cacheablility.

- Bufferability.

- Executable Never.

5.1 Sharable Region:

- Means multiple master can access the memory region (e.g. DMA and CPU).

- Strongly Ordered Memory is always sharable.

- If there is an area is cacheable and shareable, Data cache can’t be used and instruction caching can be used.

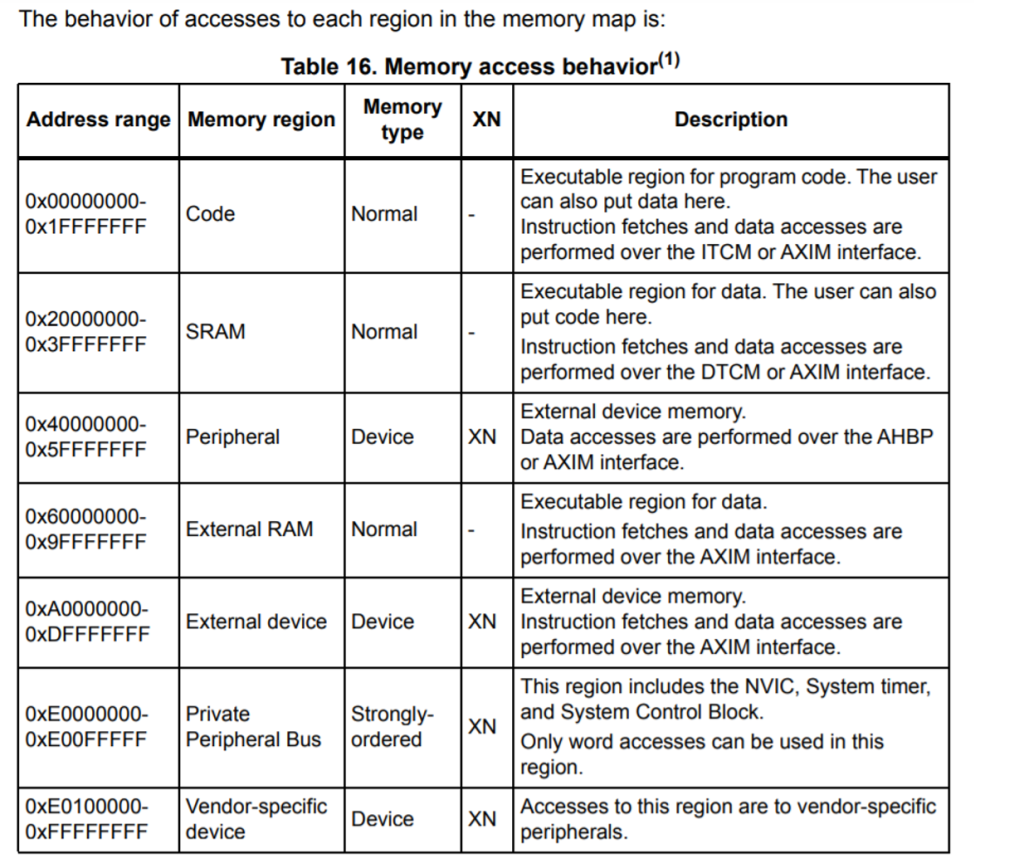

A great example for sharable region in STM32H757 is the ethernet:

Here, we are allocating 256 Byte as sharable, bufferable but not cacheable at all.

5.2 Cacheable Region:

As mentioned in the previous parts, it is the region where the caches (data and instruction) can be used.

In case multiple master is used, the cache needed to be disabled to ensure synchronous operation of multiple masters.

Later, we shall see how to configure the MPU to disable the cache for certain region.

5.3: Execute Never(XN):

This type is used to set the region where no instruction shall be executed from, trying to access this region will cause hard fault.

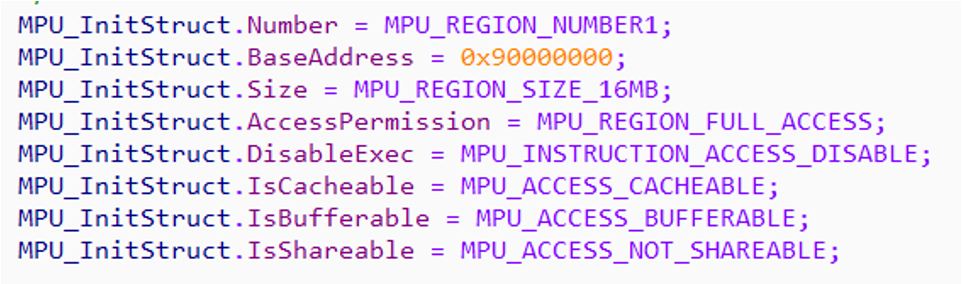

For example for NX is when to use external memory as internal flash (Memory Mapped Mode):

Here, we are setting the address to be QSPI address (0x9000 0000) and the size is 16MB which is the size of the external flash , the region is cacheable, bufferable, not shareable and instruction access is disabled (XN).

This way, if the application needed to execute an instruction from this region, it will generate hardfault.

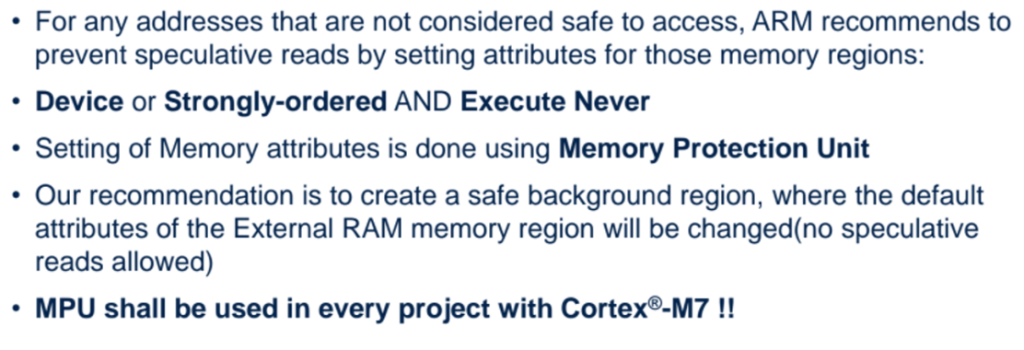

6. Important Tips:

7. MPU Configuration:

Add Comment