In this guide, we shall discuss what is SPI and how transmit single byte over SPI.

In this guide, we will cover the following:

- What is SPI.

- SPI pin setup.

- SPI initialize.

- SPI transmite function.

- Result.

1. What is SPI

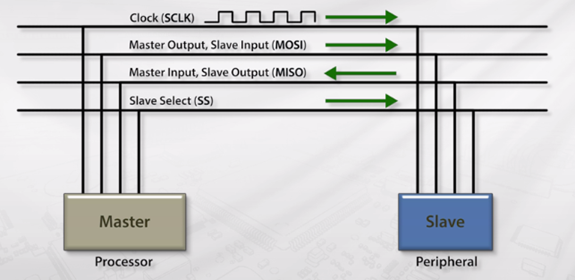

SPI, which stands for Serial Peripheral Interface, is a standard with a very specific hardware interface. A connection is between a master and a slave, with the master typical being a processor, and the slave being a peripheral such as a sensor, flash memory device, or a modem chip. It can also be used for processor to processor communications, but in this case, an additional handshake signal is often used. There are normally four signals between a master and a slave, the first is a clock signal, and this signal is always driven by the master, regard which device is transmitting. The second line is a data line for data going from the master to the slave, and this is designated as the master output, slave input line, are MOSI for short. It connects the SPI data out connection on the master and to the SPI data in connection on the slave.

The next conductor is for data in the opposite direction and is labelled as the master input slave output line, are MISO for short. The last conductor is slave select with the slave chip selecting input, and is active low.

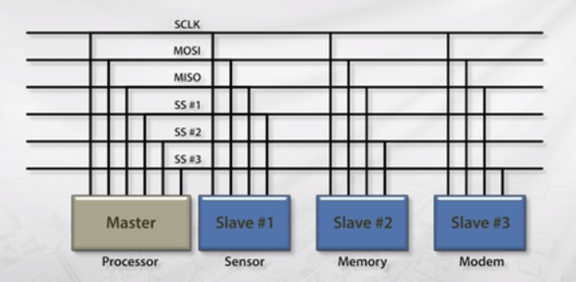

If you have more than one slave, with the first being perhaps a sensor of some kind, the slave will be dedicated to slave 1. If you add a second sensor, the top 3 interface line will be shared, but it dedicates for slave’s line will be required for the second device, and the same is true of course for each of additional slave device.

Most processors have a maxim of 4 slave selected lines. The four lines could be used effectively as a multiplexed address lines to access more than 4 slaves. You cannot have more than one master on the bus, since the interface is not support coordination between two masters as to which one is controlling the bus.

Transmissions are typically sent as a sequence of bytes, but without a formal protocol, there is nothing restricting communication being byte based. Typical by frame sizes, are in 8 to 32 bits range. Also note the bytes and packets are not acknowledged as they are in i2c, and you could have a master synching communicating with the slave but, you don’t really know of your communications are being received OK. However, some slave devices will echo bytes sent to it, which provides an acknowledgement to the master. it is how the data lines are synchronized with a clock signal.

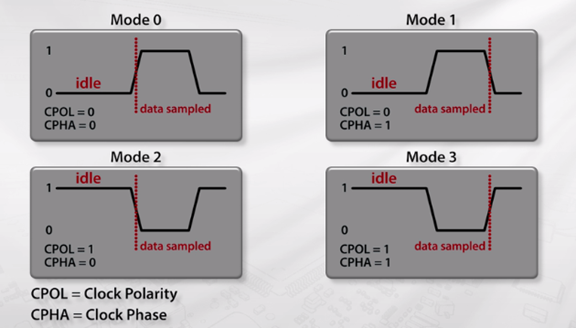

Clock Polarity and Phasing

There are four different modes available, one mode each combination clocking in a low state and high state, with a data being read in a rising edge or falling edge of the clock signal. For modes 0 and 1, the clock is low in idle, which is referred to as clock and 0, For modes 2 and 3 then the clock is in high state when idle, so it has polarity , one , For modes 0 and 2, the data will be sampled by the receiving device on the leading edge of a clock signal. Relative to the idle state, which is referred to a clock phase of zero. So for mode 0, this means the rising edge of the clock and for mode 2, means the following edge of the clock, the other two modes, use a clock phase 1 which means that trailing edge of clock as a returns to an idle state. And this translates to a following edge for mode 1 and the rising edge for mode 3. Mode 0 is the most commonly supported setting. If multiple slaves in the same bus, you may have to reconfigure the settings for the master to which modes when you want to communicate with a different slave.

2. SPI pin setup:

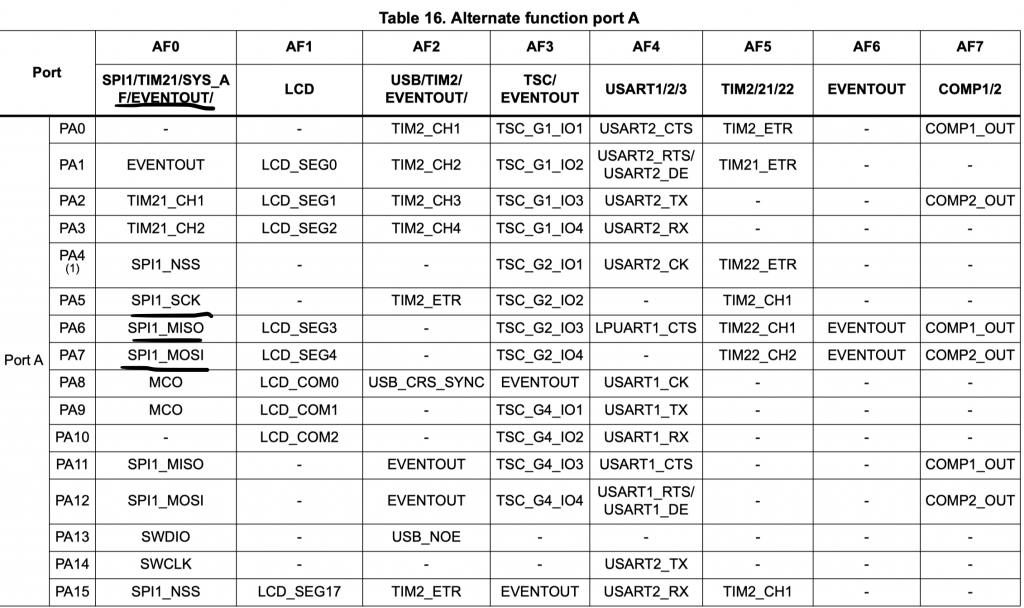

First thing first, we need to locate the pins of SPI1 in STM32L051 Nucleo-64. We can find those information in the datasheet of our microcontrol.

From the table above, we conclude that SPI has alternate function 5 and the following pins:

| Pin | SPI Function |

| PA5 | SCK (Serial Clock) |

| PA6 | MISO (Master In Slave Out) |

| PA7 | MOSI (Master Out Slave In) |

After than we can start by enabling clock access to GPIOA as following:

/*Enable clock access to GPIOA*/ RCC->IOPENR |= RCC_IOPENR_IOPAEN;

Also, set PA0 as general purpose output to toggle the CS line.

/*Set PA0 as output */ GPIOA->MODER|=(1<<0); GPIOA->MODER&=~(1<<1);

Then, set PA5,PA6 and PA7 a alternate mode:

/*Set PA5,PA6,PA7 mode to alternate function*/ /*PA5*/ GPIOA->MODER &=~(1U<<10); GPIOA->MODER |=(1U<<11); /*PA6*/ GPIOA->MODER &=~(1U<<12); GPIOA->MODER |=(1U<<13); /*PA7*/ GPIOA->MODER &=~(1U<<14); GPIOA->MODER |=(1U<<15);

Select which alternate mode(AF0):

/*Set PA5,PA6,PA7 alternate function type to SPI1 (AF0)*/ /*PA5*/ GPIOA->AFR[0] &= ~(1U<<20); GPIOA->AFR[0] &= ~(1U<<21); GPIOA->AFR[0] &= ~(1U<<22); GPIOA->AFR[0] &= ~(1U<<23); /*PA6*/ GPIOA->AFR[0] &= ~(1U<<24); GPIOA->AFR[0] &= ~(1U<<25); GPIOA->AFR[0] &= ~(1U<<26); GPIOA->AFR[0] &= ~(1U<<27); /*PA7*/ GPIOA->AFR[0] &= ~(1U<<28); GPIOA->AFR[0] &= ~(1U<<29); GPIOA->AFR[0] &= ~(1U<<30); GPIOA->AFR[0] &= ~(1U<<31);

3. Initialize SPI:

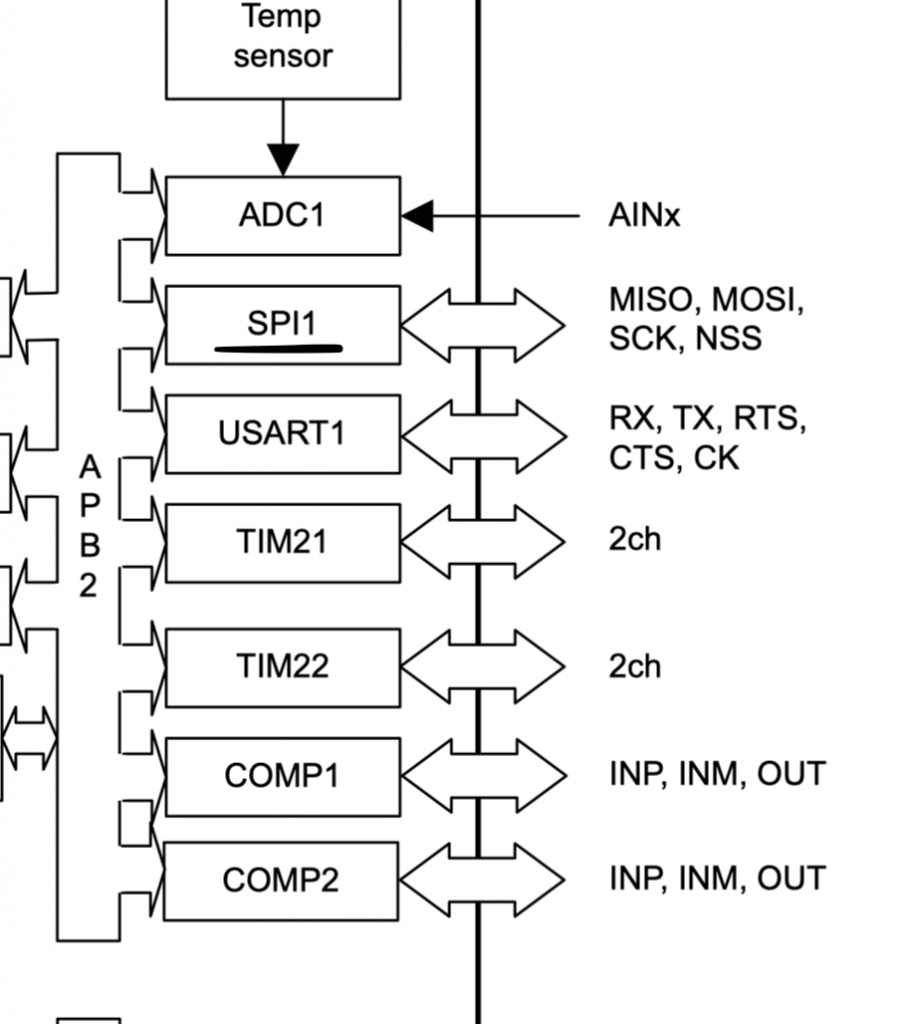

Before we initialize the SPI, we need to know which bus SPI1 is connected to:

From the datasheet, we can see that SPI is connected to APB2.

Hence, we can enable clock access to SPI as following:

/*Enable clock access to SPI1 module*/ RCC->APB2ENR |= RCC_APB2ENR_SPI1EN;

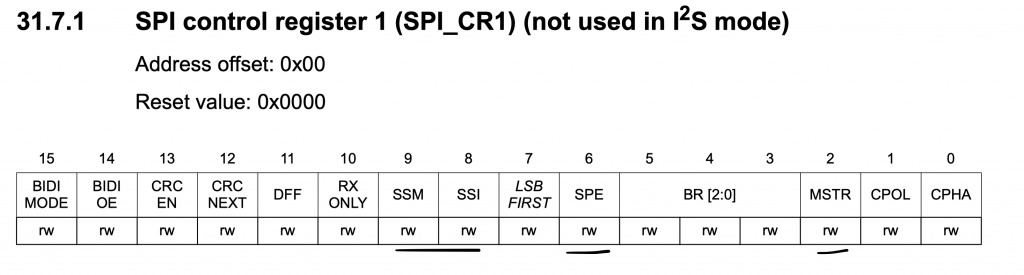

Then we set the SPI

- Set SSM and SSI

Set SPI to master mode - Finally enable SPI module

/*Set mode to MASTER*/ SPI1->CR1 |= (1U<<2); /*Select software slave management by * setting SSM=1 and SSI=1*/ SPI1->CR1 |= (1<<8); SPI1->CR1 |= (1<<9); /*Enable SPI module*/ SPI1->CR1 |= (1<<6);

4. SPI write function:

void spi_transmit(uint8_t *data,uint32_t size)

{

uint32_t i=0;

uint8_t temp;

while(i<size)

{

/*Wait for the TXE bit to set in the Status Register*/

/*This will indicate that the transmit buffer is empty*/

while (!((SPI1->SR)&(1<<1))) {};

/*Write the data to the Data Register*/

SPI1->DR = data[i];

i++;

}

/*Wait for the TXE bit to set in the Status Register*/

while (!((SPI1->SR)&(1<<1))) {};

/*Wait for the BSY bit to reset in the Status Register*/

while (((SPI1->SR)&(1<<7))) {};

/*Clear OVR flag*/

temp = SPI1->DR;

temp = SPI1->SR;

}The function takes two arguments, first pointer to the data and second one is the amount of data to be transferred.

For CS line toggle, it requires two function, cs_low and cs_high as following:

void cs_low()

{

GPIOA->BSRR=GPIO_BSRR_BR_0;

}

void cs_high()

{

GPIOA->BSRR=GPIO_BSRR_BS_0;

}Finally the SPI header file as following:

/* * spi.h * * Created on: Jul 2, 2022 * Author: hussamaldean */ #ifndef SPI_H_ #define SPI_H_ #include "stdint.h" void spi_init(); void spi_transmit(uint8_t *data,uint32_t size); void cs_low(); void cs_high(); #endif /* SPI_H_ */

In the main function:

#include "spi.h"

#include "string.h"

uint8_t data[5]={0x01,0x02,0x03,0x04,0x05};

int main(void)

{

spi_init();

while(1)

{

cs_low();

spi_transmit(data,5);

cs_high();

/*Delay a little bit*/

for (int i=0;i<10000;i++);

}

}

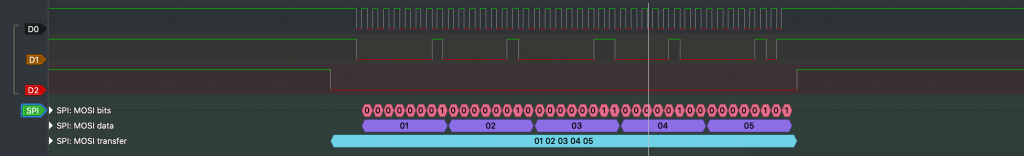

5. Results:

When you connect logic analyzer to PA5, PA7 and PA0, you will get the following results:

Happy coding 🙂

Add Comment